Zilog / IXYS Z8xC30 CMOS Serial Communications Controllers

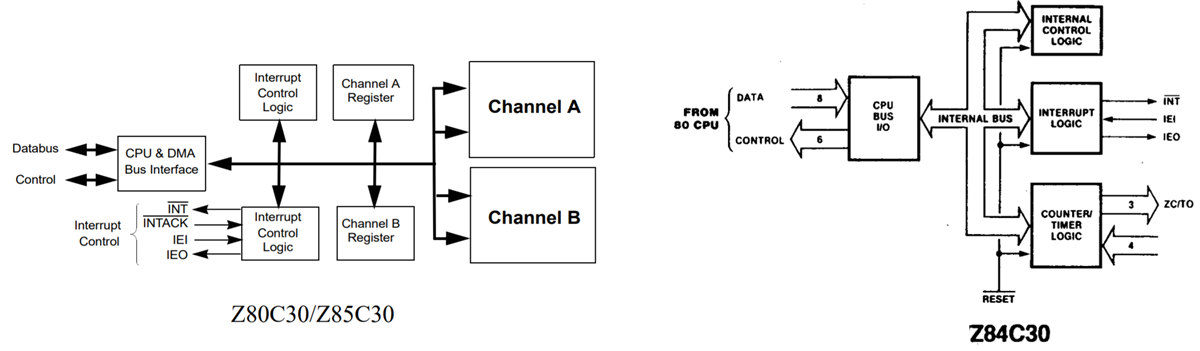

Zilog / IXYS Z8xC30 CMOS Serial Communications Controllers (SCCs) offer low power consumption, higher performance, and superior noise immunity. These SCCs include Z85C30 SCCs optimized for nonmultiplexed bus MCUs, Z80C30 SCCs optimized for multiplexed bus MCUs, and Z84C30 Counter/Timer Circuits (CTCs). The Z80C30/Z85C30 SCCs are dual-channel, multiprotocol data communications peripherals that easily interface with CPUs. Additional features include a 10x19-bit status FIFO and 14-bit byte counter to support high-speed SDLC transfers using DMA controllers. The programming flexibility of the internal registers allows the SCCs to be configured to various serial communications applications.Features

- Z85C30: optimized for nonmultiplexed bus microprocessors

- Z80C30: optimized for multiplexed bus microprocessors

- Pin-compatible to NMOS versions

- Two independent 0 to 4.1Mbps, full-duplex channels, each with separate crystal oscillator, Baud Rate Generator (BRG), and Digital Phase-Locked Loop (DPLL) for clock recovery

- Multiprotocol operation under program control; programmable for NRZ, NRZI, or FM data encoding

- Asynchronous Mode with 5 to 8 bits and 1, 1½, or 2 stop bits per character, programmable clock factor, break detection and generation; parity, overrun, and framing error detection

- Synchronous Mode with internal or external character synchronization on 1 or 2 synchronous characters and CRC generation and checking with CRC-16 or CRC-CCITT preset to either 1s or 0s

- SDLC/HDLC Mode with comprehensive frame-level control, automatic zero insertion and deletion, I-Field residue handling, abort generation and detection, CRC generation and checking, and SDLC loop

- Software interrupt acknowledge feature (not available with NMOS)

- Local Loopback and Auto Echo modes

- Supports T1 Digital Trunk76

- Enhanced DMA support (not available with NMOS), 10 x 19-bit status FIFO, and 14-bit byte counter

- Speeds:

- Z85C3O: 8.5MHz, 10MHz, and 16.384MHz

- Z80C3O: 8MHz and 10MHz

Functional Block Diagrams

發佈日期: 2021-11-15

| 更新日期: 2025-05-12