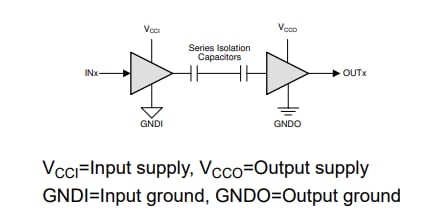

The high-performance isolators feature high electromagnetic immunity and low emissions at low power consumption while isolating CMOS or LVCMOS digital I/Os. Each isolation channel has a logic input and output buffer separated by TI's double capacitive silicon dioxide (SiO2) insulation barrier. The ISO676x is available in a variety of possible pin configurations such that all 6 channels are in the same direction, or 1, 2, or 3 channels are in reverse order. In contrast, the remaining channels are in a forward direction. The default output is high for devices without suffix F during input power or signal loss and low for devices with suffix F.

These devices help prevent noise currents on data buses, such as UART, SPI, RS-485, RS-232, and CAN, from damaging sensitive circuitry using isolated power supplies. Through innovative chip design and layout techniques, the electromagnetic compatibility of the ISO676x isolators has been dramatically enhanced to ease system-level ESD, EFT, surge, and emissions compliance.

The ISO676x family is housed in a 16-pin SOIC wide-body (DW) package and is a pin-to-pin upgrade to older generations.

Features

- 50Mbps data rate

- Robust isolation barrier:

- High lifetime at 1500VRMS working voltage

- Up to 5000VRMS isolation rating

- Up to 10kV surge capability

- ±130kV/μs typical CMTI

- Wide supply range of 1.71V to 1.89V and 2.25V to 5.5V

- 1.71V to 5.5V level translation

- Default output high (ISO676x) and low (ISO676xF) options

- Wide temperature range of –40°C to 125°C

- 1.6mA per channel typical at 1Mbps

- Low propagation delay of 11ns typical

- Robust electromagnetic compatibility (EMC)

- System-level ESD, EFT, and surge immunity

- Low emissions

- Wide-SOIC (DW-16) Package

- Safety-Related Certifications (pending):

- DIN VDE V 0884-11:2017-01

- UL 1577 component recognition program

- IEC 62368-1, IEC 61010-1, IEC 60601-1 and GB 4943.1-2011 certifications

Applications

- Power supplies

- Grid, Electricity meter

- Motor drives

- Factory automation

- Building automation

- Lighting

- Appliances

Additional Resources

Simplified Schematic

Block Diagram

5 Pin Configuration & Functions