特點

- 工業標準序列介面:

- Quad DDR (x4 xSPI) 介面:

- 命令(1位元組)= SDR

- 位址(2位元組)和資料 = DDR

- 低訊號數:

- 7個訊號腳位(CS#、SCLK、DQSM和SIO0~SIO3)

- 高效能:

- 雙倍資料速率 (DDR) 作業:

- 1.8V VCC時為200MHz (200MB/s) (1)

- 3V VCC時為133MHz (133MB/s)

- 讀取作業期間的來源同步輸出訊號 (DQSM)

- 寫入作業期間的資料遮罩 (DQSM)

- 可設定讀/寫作業的延遲

- 支援可變延遲模式和固定延遲模式

- 可設定驱动强度

- 支援包裝叢發作業模式和連續模式

- 支援深度關機模式

- 隱藏更新

- 雙倍資料速率 (DDR) 作業:

- 叢發作業:

- 可設定的繞回叢發長度:

- 16、32、64和128

- 連續作業:

- 連續讀取作業,直到陣列位址結束(未繞回)

- 連續寫入作業,甚至到陣列位址結束後(繞回到第一個位址)

- 可設定的繞回叢發長度:

- 低耗電量:

- 1.7V至1.95V單一供應電壓範圍

- 2.7V至3.6V單一供應電壓範圍

- 硬體功能:

- SCLK輸入:

- 序列時脈輸入

- SIO0 – SIO3:

- 序列資料輸入或序列資料輸出

- DQSM:

- 在命令、位址交易期間作為更新衝突指示輸出

- 在讀取資料交易期間作為讀取資料選通輸出

- 在寫入資料交易期間作為寫入資料遮罩輸入

- RESET#:

- 硬體重設腳位

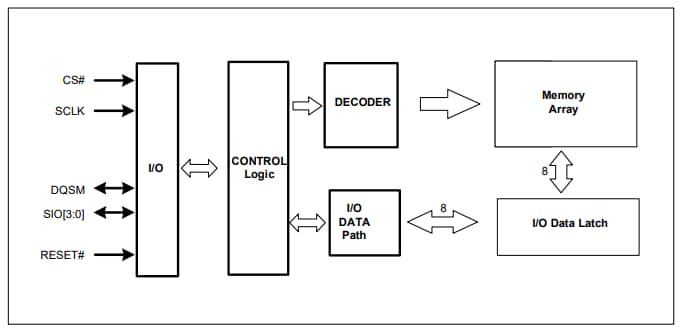

方塊圖

發佈日期: 2022-04-21

| 更新日期: 2024-03-05