Lattice Semiconductor ProcessorPM™ POWR605 PLD

Lattice ProcessorPM™ POWR605 16-Macrocell Programmable Logic Device (PLD) integrates reset generator ICs, voltage supervisor ICs, and watchdog timer ICs on one device. The ProcessorPM POWR605 features six precision programmable threshold monitors that can be configured to monitor any supply rail from 0.67V to 5.7V and a 16-Macrocell PLD that can be used for generating reset signals and brown-out signals. These ProcessorPM POWR605 PLD also includes four timers for reset pulse stretching, de-bouncing reset switches, and implementing watchdog timers. This 16-Macrocell PLD can be programmed in-system through JTAG, and the configuration is stored in the on-chip non-volatile E2CMOS® memory. The ispPAC®-POWR607 is an evaluation kit that demonstrates the functions of the POWR605 PLD.Features

- Precision Programmable Threshold Monitors, Threshold Accuracy 0.7%

- Simultaneously monitors up to six power supplies

- Programmable analog trip points (1% step size; 192 steps)

- Programmable glitch filter

- Power-off detection (75mV)

- Embedded Programmable Timers

- Four independent timers

- 32µs to 2-second intervals for timing sequences

- Embedded PLD for Logical Control

- Rugged 16-macrocell CPLD architecture

- 81 product terms / 28 inputs

- Implements state machines and combinatorial functions

- Power-Down Mode ICC < 10µA

- Digital I/O

- Two dedicated digital inputs

- Five programmable digital I/O pins

- Wide Supply Range (2.64V to 3.96V)

- In-system programmable through JTAG

- Industrial temperature range: –40°C to +105°C

- 24-pin QFN package, lead-free option

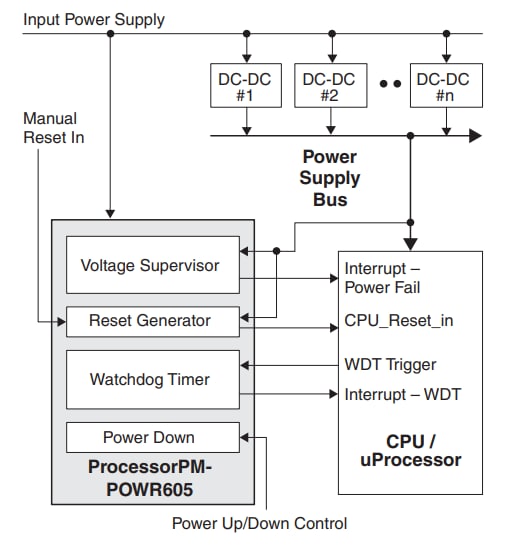

Block Diagram

發佈日期: 2009-04-30

| 更新日期: 2022-03-11