|

Analog Devices HMC7043時脈緩衝器概觀 |

|

產品特色

應用

|

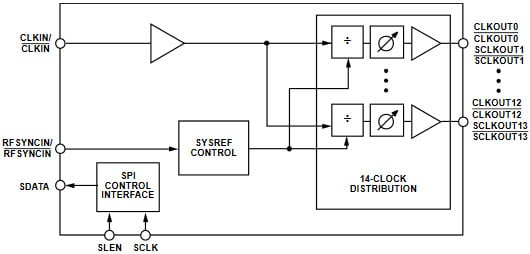

功能方塊圖 |

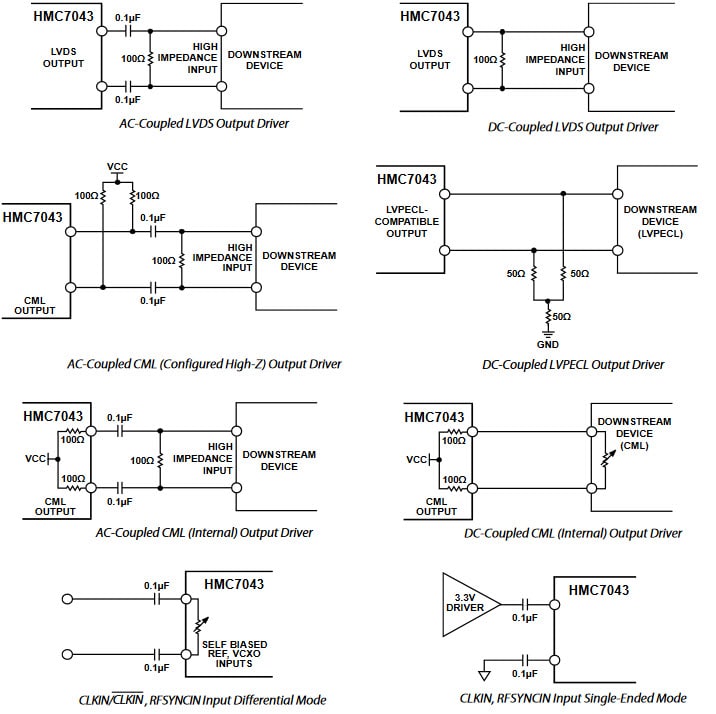

典型應用電路  |

EK1HMC7043LP7評估套件EK1HMC7043LP7評估套件設計為小型易用的平台,可協助設計人員評估HMC7043時脈緩衝器的功能。 評估套件內容

|

|

發佈日期: 2016-08-08

| 更新日期: 2022-03-11

香港

香港|

港幣

國際貿易術語:貨交承運人(裝運地點) 關稅、海關手續費和貨物服務稅在交貨時收取。 大多數訂單滿HK$330 (HKD)即可免運費。 |

|

美元

國際貿易術語:貨交承運人(裝運地點) 關稅、海關手續費和貨物服務稅在交貨時收取。 大多數訂單滿$50 (USD)即可免運費。 |

|

Analog Devices HMC7043時脈緩衝器概觀 |

|

產品特色

應用

|

功能方塊圖 |

典型應用電路  |

EK1HMC7043LP7評估套件EK1HMC7043LP7評估套件設計為小型易用的平台,可協助設計人員評估HMC7043時脈緩衝器的功能。 評估套件內容

|

|