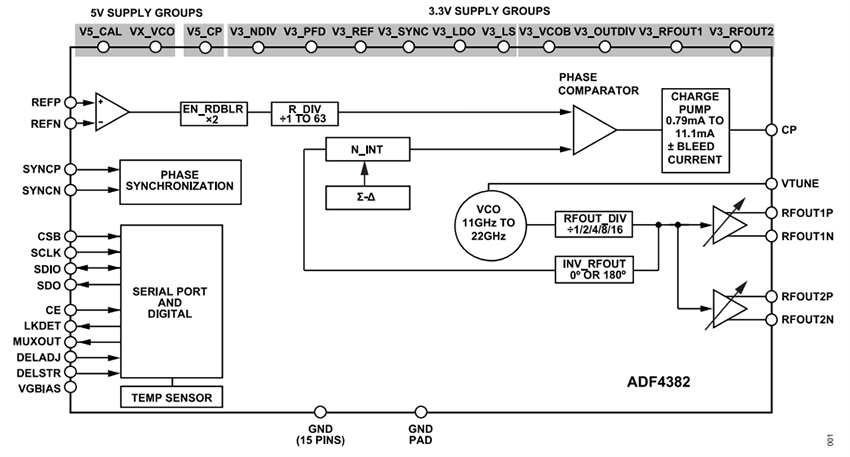

Analog Devices Inc. ADF4382x分數-N型鎖相迴路 (PLL)

Analog Devices ADF4382x分數-N型鎖相迴路 (PLL) 是一款高性能、超低抖動的分數-N型鎖相迴路 (PLL)。其整合的電壓控制振盪器 (VCO) 非常適合用於5G或資料轉換器時鐘應用之本地振盪器 (LO) 生成功能。高性能PLL的品質因數為-239dBc/Hz,1/f噪音低,整數模式下高PFD頻率為625MHz,可實現超低頻內雜訊和整合抖動。ADF4382x可產生11.5GHz至21GHz的基倍頻範圍内的頻率,無需使用次諧波濾波器。ADF4382x上的二分之一和四分之一輸出分頻器可分別產生5.75GHz至10.5GHz和2.875GHz至5.25GHz的頻率。Analog Devices ADF4382x將輸出分頻器納入PLL回饋迴圈,自動將輸出對齊輸入參考邊緣,適用於多個資料轉換器時脈應用。提供可程式參考以輸出延遲,解析度低於1ps,適用於需要確定性延遲或延遲調整功能的應用。參考輸出延遲匹配多個裝置和過熱,可實現可預測且精確的多晶片時脈和系統參考 (SYSREF) 對齊。ADF4382x區塊圖的簡潔性,簡化了串聯周邊介面 (SPI) 暫存器映射,可重複多晶片時脈對齊,並透過允許在晶片外生成SYSREF,限制不必要的時鐘脈衝,從而縮短開發時間。

特點

- 輸出頻率範圍為687.5MHz至22GHz

- 20GHz整合式RMS抖動

- 20fs(整合頻寬:100Hz至100MHz)

- 31fs(ADC SNR法)

- 快速<1μs VCO校正時間

- <100μs VCO自動校正時間

- -156dBc/Hz在20GHz的相位噪聲底層

- PLL規格

- -239dBc/Hz帶內標準化相位噪聲底層

- -287dBc/Hz 1/f標準化相位噪聲底層

- 625MHz最大相位/頻率偵測器輸入頻率

- 4.5GHz參考輸入頻率

- -90dBc典型寄生頻率PFD

- 參考輸出延遲規格

- 0.06ps/°C傳播延遲溫度係數

- <1ps調整步驟尺寸

- 多晶片輸出相位對齊

- 3.3V和5V電源

- ADIsimPLL™迴路濾波器設計工具支援

- 7mm × 7mm,48觸點LGA封裝

- 操作溫度範圍:-40°C至+105°C

應用

- 高性能資料轉換器計時

- 無線基礎架構(MC-GSM、5G、6G)

- 測試與量測業

功能方塊圖

發佈日期: 2024-07-05

| 更新日期: 2025-06-20