AD7768提供高速、中等和節電模式供設計人員選擇,可選出最佳的雜訊效能與耗電量組合。AD7768 ADC有三種功率模式可選,能為低功耗DC和高效能AC測量模組提供可重複使用的平台。

AD7768 ADC也提供多樣化的數位濾波功能、經由sinc5濾波器的sinc響應、適用於低頻寬的低延遲路徑,以及低雜訊測量等功能。

特點

- 精準的AC與DC效能

- 8/4通道同步取樣

- 每通道256 kSPS ADC輸出資料速率

- 108 dB動態範圍

- 110.8kHz輸入頻寬 (BW)(−3dB頻寬)

- −120dB總諧波失真 (THD) 典型值

- ±2 ppm完整測量範圍 (FSR) 積分非線性 (INL)、±50 μV偏移誤差、±30 ppm增益誤差

- 最佳化的功率消耗和雜訊與輸入頻寬組合

- 可選擇功率、速度和輸入頻寬

- 高速:速度最快;110.8 kHz頻寬,每通道51.5 mW

- 中等:中等速度;55.4 kHz頻寬,每通道27.5 mW

- 節電:耗電最少;13.8 kHz頻寬,每通道9.375 mW

- 可選擇功率、速度和輸入頻寬

- 輸入頻寬範圍:DC至110.8 kHz

- 可程式輸入頻寬/取樣速率

- 資料介面的循環冗餘檢查 (CRC) 錯誤檢查

- 適用於菊鏈

- 線性相位數位濾波器

- 低延遲sinc5濾波器

- 寬頻磚牆式濾波器:±0.005 dB漣波至102.4 kHz

- 類比輸入預充電緩衝器

- 電源供應器

- AVDD1 = 5V,AVDD2 = 2.25V至5V

- IOVDD = 2.5V至3.3V,或IOVDD = 1.8V

- 64導線LQFP封裝,無腳墊

- 溫度範圍:-40°C至+105°C

應用

- 資料擷取系統:USB/PXI/乙太網路

- 儀器和工業控制迴路

- 音訊測試與測量

- 震動與資產條件監控

- 三相電源品質分析

- 聲納

- 高精度醫療用EEG/EMG/ECG

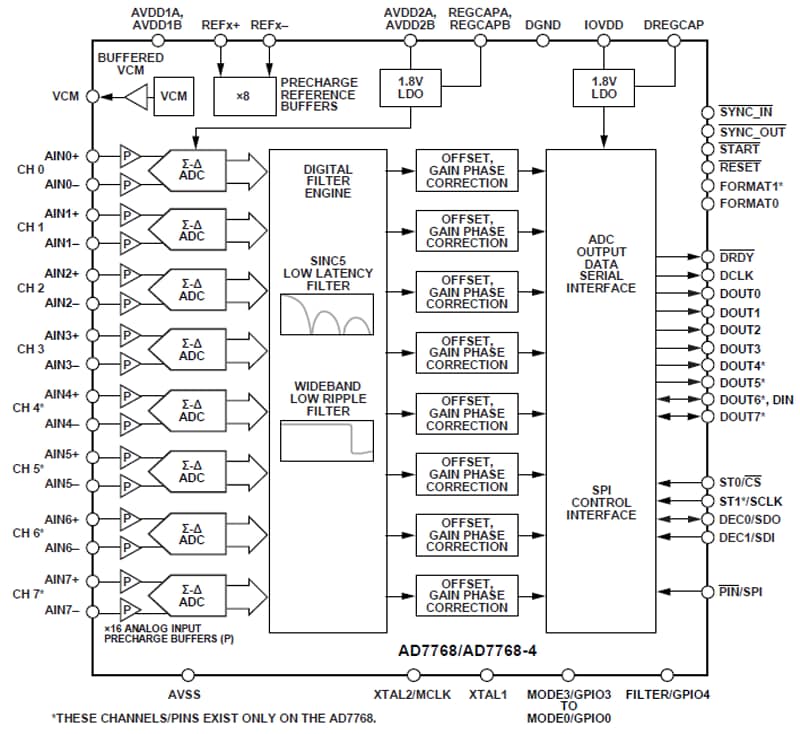

方塊圖

其他資源

- Understanding and Extending Safety Operation in a Sigma-Delta ADC

- Application Note

- How High Performance Modular Instruments Enable Greater Applications and Smaller Form Factor

- No Infidelity: Audio Test Platforms Benefit from New 24-Bit, Sigma-Delta ADC’s Superior SINAD

- Sigma-Delta ADC Clocking - More Than Jitter

- Article - Maximize the Performance of Your Sigma-Delta ADC Driver

技術文章

-

Precision data acquisition for Seismology and Energy Exploration

This article discusses how to design a low noise and low power DAQ solution for seismology and energy exploration.

Learn More - Understanding the Fundamentals of Earthquake Signal Sensing Networks

Modern, low cost MEMs based ground sensing technology is now capable of measurements that are on par with traditional instruments. Using the wide range of Analog Devices products, a sensing device can be implemented to cater different seismic sensing applications.

Learn More -

Condition-Based Monitoring: The Wearable for Machine Health

Condition-based monitoring (CbM) is the Industry 4.0 equivalent of wearable fitness devices. With the explosion of connectivity comes the opportunity to observe the physical world like never before and to see physical processes in action, in real time, in fine detail. Reduce unplanned downtime by understanding the aging process of equipment and machines.

Learn More -

Sigma-Delta ADC Clocking—More Than Jitter

One of the key benefits of modern SAR and Σ-Δ analog-to-digital converters (ADCs) is that they are designed with ease of use in mind. A single reference design to be used and recycled for multiple generations and across a great variety of applications. In the rush to reuse and complete designs, precision performance is often sacrificed. One of the primary oversights and areas of neglect is in clocking. In this article, we will discuss the importance of the clock and offer guidance on proper designs for high performance converters.

Learn More